Разработчики GCC выпустили обновление под кодовым именем «znver6», предназначенное для добавления совместимости с перспективной микроархитектурой Zen 6 от AMD.

Данное обновление также проливает свет на базовую систему инструкций (ISA) для Zen 6, в которую войдут следующие расширения:

- AVX512_FP16

- AVX_NE_CONVERT

- AVX_IFMA

- AVX_VNNI_INT8

Хотя современные решения Zen уже имеют поддержку AVX512, внедрение AVX-512 FP16 значительно расширит функционал будущих поколений архитектуры. Также ожидается интеграция VNNI INT8 в новый набор команд.

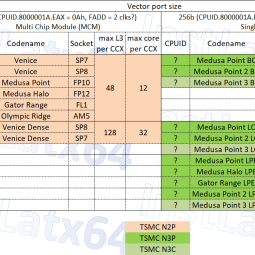

Энтузиаст @InstLatX64 выявил новый идентификатор B80F00, относящийся к одному из семейств Zen 6. Серверная линейка Venice, как ожидается, будет включать две модификации: Classic и Dense. Артикулы Venice Classic — SP7 «B50F00» и SP8 «B90F00», тогда как Venice Dense обозначены как SP7 «BC0F00» и SP8 «BA0F00».

В классической версии каждый CCX-модуль будет содержать до 12 ядер, а в плотной — до 32 ядер. Планируется, что топовые конфигурации Venice будут оснащаться 256 ядрами (8 модулей CCX) с кэшем L3 объёмом до 1024 МБ в Dense-версии за счёт 128 МБ на каждый модуль.

Для потребительского сегмента готовится как минимум четыре семейства Zen 6. Это включая флагманскую платформу AM5 «Olympic Ridge» с 24 ядрами и 48 потоками (12 ядер и 48 МБ L3 на CCX), а также решения Gator Range, Medusa Point и Medusa Halo. MCM-решения будут производиться по техпроцессу TSMC N2P, тогда как монолитные APU линейки Medusa Point и Gator Range могут использовать TSMC N3P/N3C.

Официальная презентация архитектуры Zen 6 запланирована на выставку CES 2026.